# PDP-9/L USER HANDBOOK

**JUNE 1968**

# TABLE OF CONTENTS

| Chapter |                                                | Page                   | Chapter |                                                  | Page         |

|---------|------------------------------------------------|------------------------|---------|--------------------------------------------------|--------------|

| 1       | SYSTEM INTRODUCTION                            |                        | 3       | Memory Extension Control,                        |              |

|         | General                                        | 1-1                    | (con't) | Type KG09A                                       | 3-5          |

|         | Characteristics                                | 1-1                    |         | Additional Core Memory Power Failure Protection, | 3-5          |

|         | Design<br>Configurations                       | 1-3<br>1-3             |         | Type KP09A                                       | 3-5          |

|         | Configurations                                 | 1-3                    |         | Memory Protection Option,                        | 3-3          |

| 2       | SOFTWARE SYSTEM                                |                        |         | Type KX09A                                       | 3-5          |

|         | General                                        | 2-1                    |         | Automatic Priority Interrupt,                    |              |

|         | PDP-9/L Compact Software                       | 2-1                    |         | Type KF09A                                       | 3-8          |

|         | Assembler                                      | 2-1                    |         |                                                  |              |

|         | Symbolic Editor                                | 2-1                    |         |                                                  |              |

|         | ODT-9<br>TRACE-9                               | 2-2<br>2-2             | 4       | PERIPHERALS                                      |              |

|         | SCAN                                           | 2-2<br>2-2             | 7       | General                                          | 4-1          |

|         | FAST-9                                         | 2-2                    |         | Standard Input/Output Equip-                     | 7-1          |

|         | HRM-Puncher                                    | $\frac{2}{2}$ -2       |         | ment                                             | 4-1          |

|         | Floating Point Package                         | 2-3                    |         | Keyboard                                         | 4-1          |

|         | Integer Arithmetic                             | 2-3                    |         | Reader                                           | 4-1          |

|         | FLIO                                           | 2-3                    |         | Teleprinter                                      | 4-2          |

|         | TOD                                            | 2-3                    |         | Punch                                            | 4-2          |

|         | TTYIO                                          | 2-3                    |         | Optional Peripherals                             | 4-2          |

|         | DIP-OPS<br>DTLIST                              | 2-3<br>2-3             |         | Teletype Model 33 KSR and<br>Control             | 4-2          |

|         | MTDUPE                                         | 2-3<br>2-3             |         | Keyboard                                         | 4-2<br>4-3   |

|         | Trig Functions                                 | 2-3                    |         | Perforated Tape Reader Type                      | 7-3          |

|         | PDP-9/L Advanced Software                      | 2-3                    |         | PC09A                                            | 4-3          |

|         | Paper Tape (or Card) System                    | 2-3                    |         | Perforated Tape Punch                            | 4-5          |

|         | Device-Independent System                      | 2-4                    |         | Card Reader and Control                          |              |

|         | System Components                              | 2-4                    |         | Type CR02B                                       | 4-7          |

|         | FORTRAN                                        | 2-4                    |         | Automatic Sine Printer                           |              |

|         | Macro Assembler                                | 2-4                    |         | Type 647                                         | 4-8          |

|         | Debugging System (DDT-9)                       | 2-5                    |         | Incremental Plotter and Contro<br>Type 350       | 4-11         |

|         | Symbolic Editor Peripheral Interchange Program | 2-5                    |         | Oscilloscope Display Type 34H                    |              |

|         | (PIP-9)                                        | 2-5                    |         | Precision CRT Display Type                       | 4-14         |

|         | Linking Loader                                 | 2-6                    |         | 30D                                              | 4-14         |

|         | Input/Output Programming                       |                        |         | Photomultiplier Sight Pen                        |              |

|         | System (IOPS)                                  | 2-6                    |         | Type 370                                         | 4-14         |

|         | Input/Output Monitor                           | <b>2-</b> 6            |         | Analog to Digital Converter                      |              |

|         | Keyboard Monitor (KM-9)                        | 2-6                    |         | and Multiplier Type AF01B                        | 4-14         |

|         | Expansion of PDP-9 Advanced                    | 0.7                    |         | Digital to Analog Converter                      | 4.16         |

|         | Software System MAINDEC Diagnostic Programs    | 2-7                    |         | Type AA01A<br>Multistation Teletype Control      | 4-16         |

|         | MAINDEC Diagnostic Programs                    | 2-7                    |         | Type LT09A                                       | 4-17         |

| 3       | SYSTEM ORGANIZATION                            |                        |         | Relay Buffer Type DR09A                          | 4-18         |

| J       | General                                        | 3-1                    | •       | Interprocessor Buffers DB99A                     |              |

|         | Central Processor Unit                         | 3-1                    |         | and DB98A                                        | 4-18         |

|         | Core Memory                                    | 3-2                    |         | Command Status Register Con <sub>7</sub>         |              |

|         | Input/Output Facilities                        | 3-2                    |         | figuration                                       | 4-18         |

|         | Program Controlled Transfers                   | 3-3                    |         | PDP-9/L to PDP-7 Inter-                          | 4.00         |

|         | Conditional Skip on Device Status              | 3-3                    |         | processor Buffer Type DB97A                      | 4-20         |

|         | Input/Output Read Status                       | 3-3                    |         | Data Communications System                       | 4-20         |

|         | Program Interrupt<br>Data Channels             | 3-3<br>3-4             |         | Type DP09A (DP01B) Transmit Flag                 | 4-20<br>4-21 |

|         | Add-to-Memory Capability                       | 3-4<br>3-4             |         | Receive Flag                                     | 4-21         |

|         | Options Capability                             | 3 <del>-4</del><br>3-5 |         | Receive Flag Receive End Flag                    | 4-21         |

|         | Extended Arithmetic Element,                   | 55                     |         | Ring Flag                                        | 4-21         |

|         | Type KE09A                                     | 3-5                    |         | Data Set Ready Flag                              | 4-21         |

# TABLE OF CONTENTS (continued)

| Chapter |                                   | Page            | Chapter     |                                             | Page         |

|---------|-----------------------------------|-----------------|-------------|---------------------------------------------|--------------|

| 5       | AUXILIARY STORAGE SYSTEMS         |                 | 8           | Scaling for Fixed Point Arith-              |              |

|         | General                           | 5-1             | (continued) | metic                                       | 8-3          |

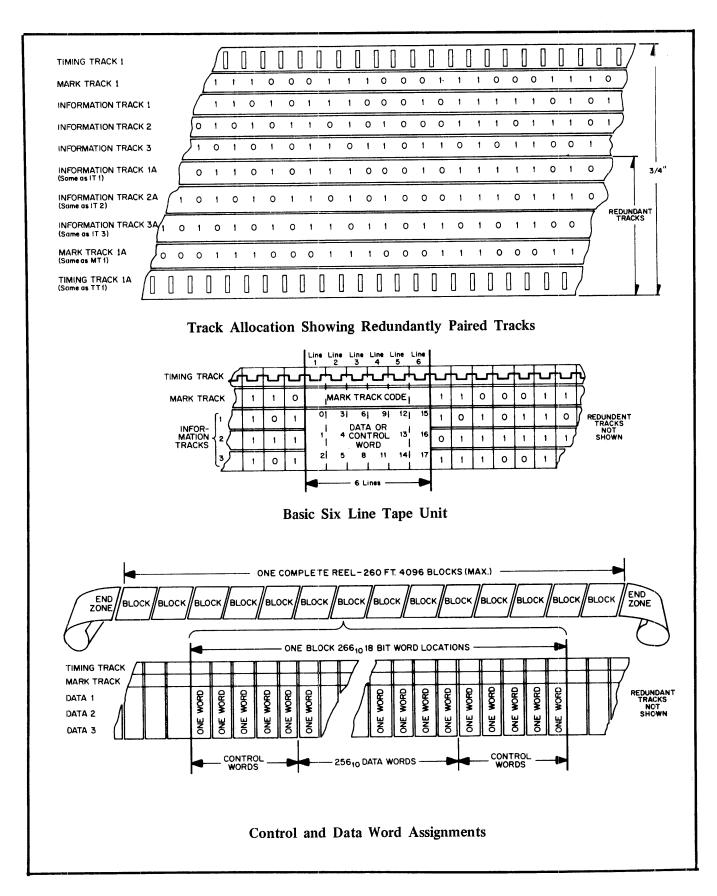

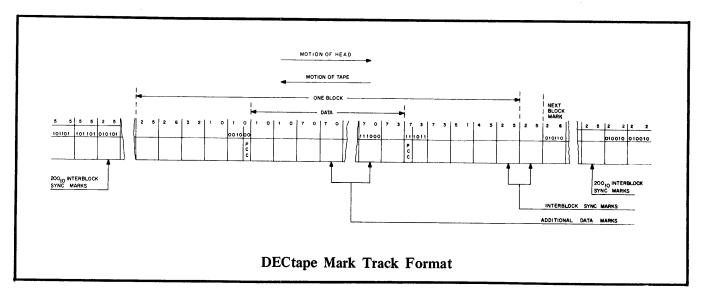

|         | DECtape System                    | 5-1             |             | Addition and Subtraction                    | 8-4          |

|         | DEĈtape Format                    | 5-1             |             | Multiplication                              | 8-5          |

|         | DECtape Transport Type TU55       | 5-1             |             | Division                                    | 8-5          |

|         | DECtape Control Type TC02         | 5-1             |             | Scaling on a Binary Computer                | 8-5          |

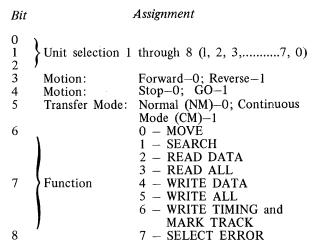

|         | Command and Status Bit con-       |                 |             | Overflow                                    | 8-6          |

|         | figuration                        | 5-4             |             | Programming Techniques for                  |              |

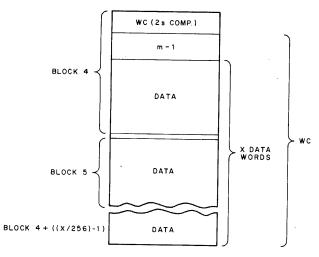

|         | DECtape System Programming        |                 |             | Scaling                                     | 8-6          |

|         | Information                       | 5-5             |             | Analysis                                    | 8-6          |

|         | DECtape Programming Examples      |                 |             | Addition Scaling                            | 8-7          |

|         | Magnetic Tape Control, Type       |                 |             | Multiplication Scaling                      | 8-7          |

|         | TC59                              | 5-12            |             | Division Scaling                            | 8-8          |

|         |                                   | 5-16            |             | Fixed Point Addition                        | 8-8          |

|         | Magnetic Tape Functions           | 5-18            |             | Fixed Point Subtraction                     | 8-8          |

|         | 9-Track Operation                 |                 |             | Tined Tollie Subtraction                    | 0.0          |

|         | Status or Error Conditions        | 5-18            | 9           | INPUT/OUTPUT CONSIDERATIONS                 |              |

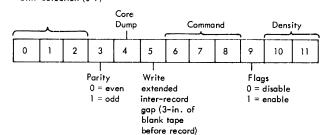

|         | Command Register Contents         | 5-20            |             | General                                     | 9-1          |

|         | Magnetic Tape Function Sum-       | 5.20            |             | Program Controlled Transfers                | 9-1          |

|         | mary                              | 5-20            |             | Input/Output Read Status                    | )-1          |

|         | Magnetic Tape Transport, Type     | <b>5.0</b> 0    |             | Facility                                    | 9-2          |

|         | TU20 (7-CHANNEL)                  | 5-20            |             | Input/Output Skip Facility                  | 9 <b>-</b> 2 |

|         | Magnetic Tape Transport, Type     |                 |             | Program Interrupt Control                   | 9-4          |

|         | TU20A (9-CHANNEL)                 | 5-21            |             | Automatic Priority Interrupt                | 9-6          |

|         | , DDDEGGNIG                       |                 |             | Priority Level                              | 9-7          |

| 6       | ADDRESSING                        |                 |             | Channels                                    | 9-7<br>9-7   |

|         | General                           | 6-1             |             | API IOT Instructions                        | 9-7<br>9-7   |

|         | Direct Addressing                 | 6-1             |             | Dynamic Priority Reallocation               | 9-7<br>9-7   |

|         | Indirect Addressing               | 6-1             |             |                                             | 9-7          |

|         | Autoindexing                      | 6-2             |             | Programming Examples Que-                   | 9-11         |

|         | Extend Mode Addressing            | 6-3             |             | ueing<br>Data Channel Transfers             |              |

|         | Reserved Addresses                | 6-4             |             |                                             | 9-11<br>9-13 |

|         |                                   |                 |             | Add-To-Memory Capability<br>Real-Time Clock |              |

| 7       | INSTRUCTIONS                      |                 |             | Real-Time Clock                             | 9-13         |

|         | General                           | 7-1             | 10          | CONTROLS AND INDICATORS                     |              |

|         | Memory Reference Instruction      |                 | 10          |                                             | 10-1         |

|         | Format                            | 7-1             |             | Operator Console                            |              |

|         | Augmented Instruction Format      | 7-1             |             | Marginal Check Panel                        | 10-1         |

|         | Memory Reference Instructions     | 7-2             |             | DEPOSITORIONI TO INTEREACINA                | <u></u>      |

|         | Operate Instructions              | 7 <del>-4</del> | 11          | INTRODUCTION TO INTERFACING                 |              |

|         | Input/Output Transfer Instruction | ns 7-8          |             | General                                     | 11-1         |

|         | Clear All Flags                   | 7-10            |             | Circuit Modules for Interfacing             | 11-1         |

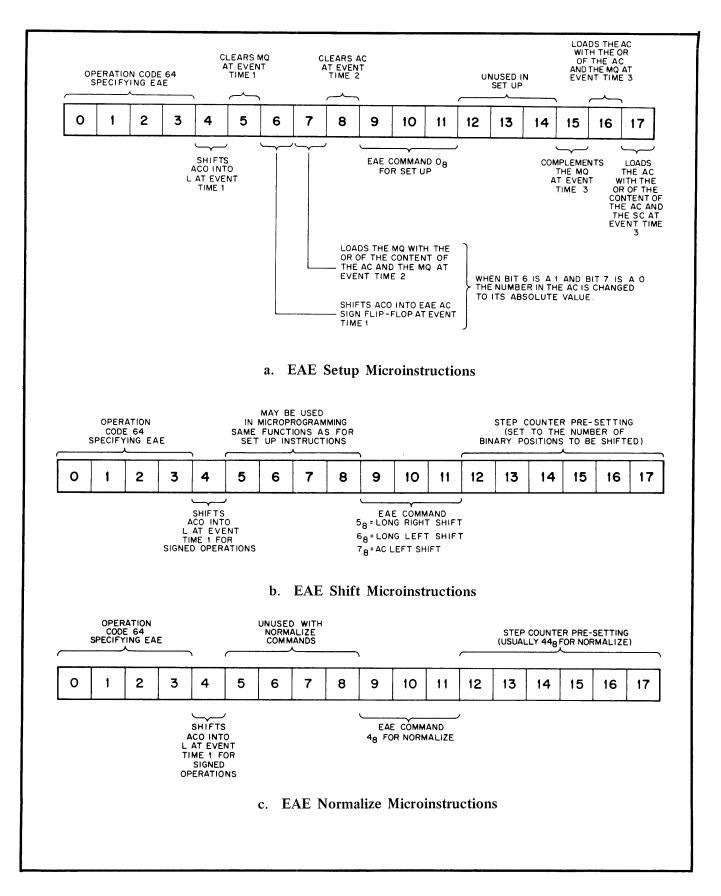

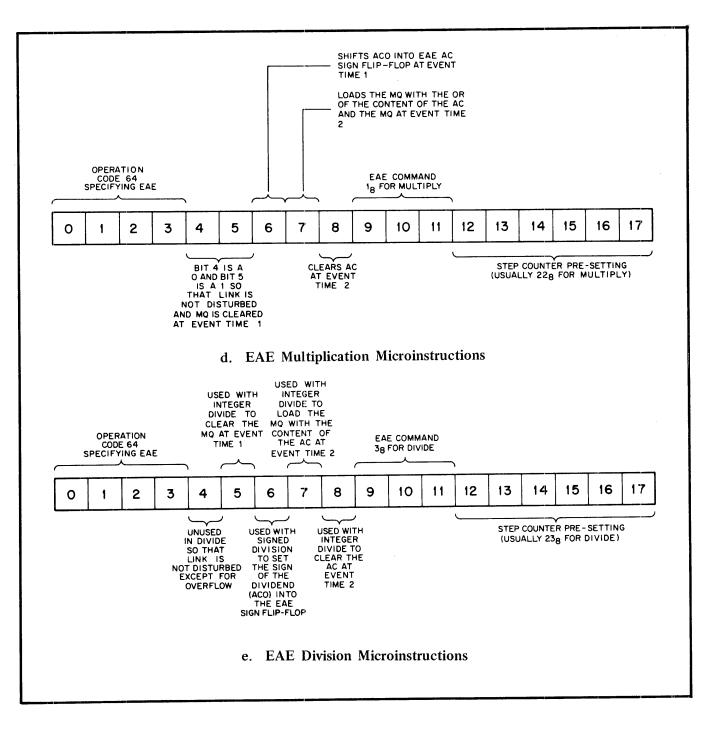

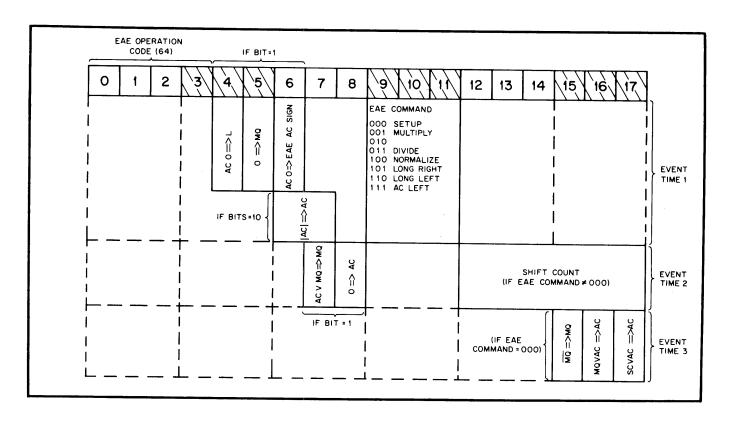

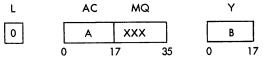

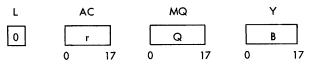

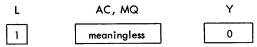

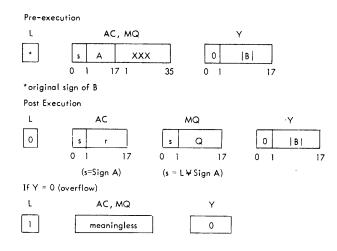

|         | EAE Instructions                  | 7-10            |             | Logic Symbols                               | 11-1         |

|         | EAE Setup                         | 7-10            |             | I/O Communications                          | 1.1-1        |

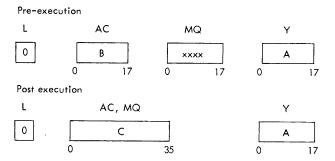

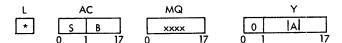

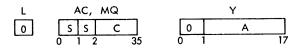

|         | EAE Shifting Instructions         | 7-14            |             |                                             |              |

|         | EAE Arithmetic Instructions       | 7-17            |             | THE I/O DIE                                 |              |

|         |                                   |                 | 12          | THE I/O BUS                                 |              |

| 8       | DATA FORMATS AND ARITH-           |                 |             | General                                     | 12-1         |

|         | METIC INFORMATION                 |                 |             | Physical Description                        | 12-1         |

|         | General                           | 8-1             |             | I/O Power                                   | 12-2         |

|         | Signed Data Notations             | 8-1             |             | Interface Signals                           | 12-2         |

|         | Signed and Magnitude Notatio      | n 8-1           |             | Data Lines                                  | 12-2         |

|         | Complement Notation               | 8-1             |             | Output Control Signals                      | 12-2         |

|         | Data Words                        | 8-2             |             | Device Selection Levels                     | 12-3         |

|         | Data Word Formats                 | 8-2             |             | I/O Run                                     | 12-3         |

|         | Magnitudes of Data Words          | 8-2             |             | Input Control Levels                        | 12-3         |

|         | Basic Software Floating-Point     |                 |             | Multiplexed Control Lines                   | 12-4         |

|         | Formats                           | 8_3             |             | Address Lines                               | 12-4         |

# TABLE OF CONTENTS (continued)

| Chapter           | •                                                              | Page         | Chapter           |                                                                                                                      | Page                 |

|-------------------|----------------------------------------------------------------|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|

| 12<br>(continued) | Driving Address and Data<br>Lines<br>I/O Bus Interface Summary | 12-4<br>12-4 | 14<br>(continued) | Initial Sequence of Data-Out<br>Transfer (From Computer)<br>Operations Unique to Writ-<br>ing (Refer to Figure 14-4) | 14-4<br>14-4         |

| 13                | PROGRAM CONTROLLED                                             |              |                   | Expansion to Eight Devices                                                                                           |                      |

|                   | TRANSFERS<br>General                                           | 12.1         |                   | Signal Definitions                                                                                                   | 14-4                 |

|                   | Input/Output Transfer Instruc-                                 | 13-1         |                   | Add-To-Memory Capabilities<br>Standard Core Register Assign-                                                         | 14-4                 |

|                   | tions                                                          | 13-1         |                   | ment                                                                                                                 | 14-5                 |

|                   | Reading a Device Buffer into                                   |              |                   |                                                                                                                      | 113                  |

|                   | the AC                                                         | 13-5         | 15                | INSTALLATION PLANNING                                                                                                |                      |

|                   | Loading a Device Buffer                                        | 40.5         |                   | General                                                                                                              | 15-1                 |

|                   | from the AC                                                    | 13-5         |                   | Placement of Options                                                                                                 | 15-2                 |

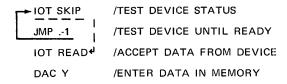

|                   | I/O Skip Facility Status Word Facility                         | 13-6<br>13-6 |                   | Environmental Requirements                                                                                           | 15-5                 |

|                   | Program Interrupt (PI) Facility Automatic Priority Interrupt,  | 13-7         |                   | Power Requirements Cabling Requirements Adding Special Interfaces                                                    | 15-6<br>15-6<br>15-7 |

|                   | Type KF09A                                                     | 13-8         |                   | Adding Special Interfaces                                                                                            | 13-7                 |

| 14                | DATA CHANNEL                                                   |              |                   |                                                                                                                      |                      |

|                   | General                                                        | 14-1         |                   |                                                                                                                      |                      |

|                   | Latency                                                        | 14-1         | Appendix          |                                                                                                                      |                      |

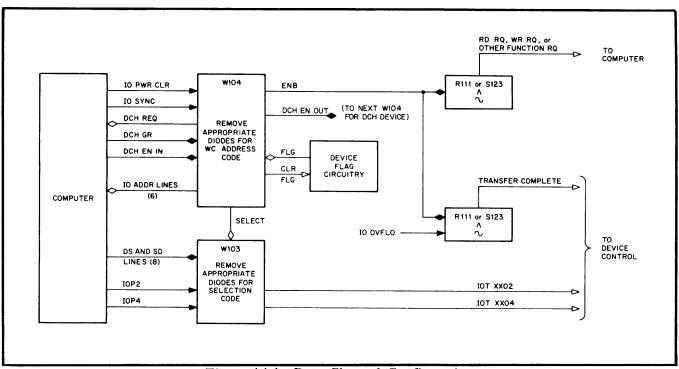

|                   | Device Interface Hardware                                      | 14-2         | 1                 | INICTRICATION CHAMARY                                                                                                |                      |

|                   | Initial Sequence of Data-In                                    | 140          | 1                 | INSTRUCTION SUMMARY                                                                                                  |                      |

|                   | Transfer (To Computer) Operations Unique to                    | 14-2         | 2                 | PDP-9 I/O CODES                                                                                                      |                      |

|                   | Reading (Refer to figure 14-3)                                 | 14-4         | 3                 | SCALES OF NOTATION                                                                                                   |                      |

# LIST OF ILLUSTRATIONS

| Figure      | Title                                                                        | Page         |

|-------------|------------------------------------------------------------------------------|--------------|

| 1-1         | Basic PDP-9/L                                                                | 1-3          |

| 1-2         | Expanded PDP-9/L System Configuration, Block Diagram                         | 1-3          |

| 3-1         | Central Processor-Major Register Organization                                | 3-1          |

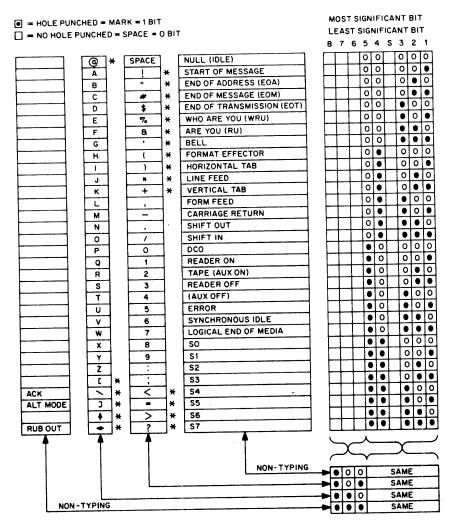

| 4-1         | Perforated Tape Format                                                       | 4-4          |

| 5-1         | DECtape Format (Sheet 1)                                                     | 5-2          |

|             | DECtape Format (Sheet 2)                                                     | 5-3          |

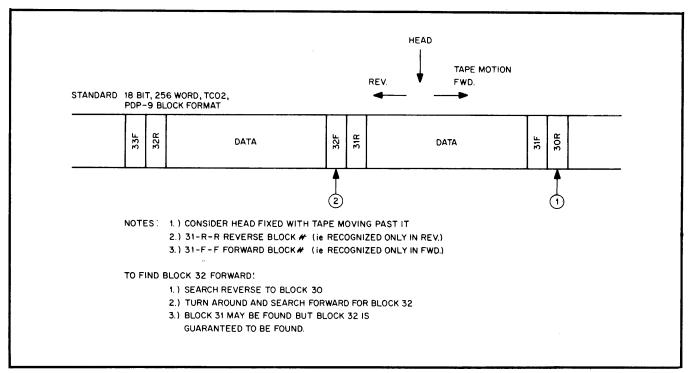

| 5-2         | Location of Block in Opposite Direction                                      | 5-13         |

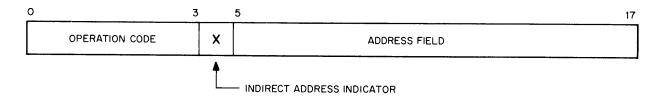

| 7-1         | Memory Reference Instruction Format                                          | 7-1          |

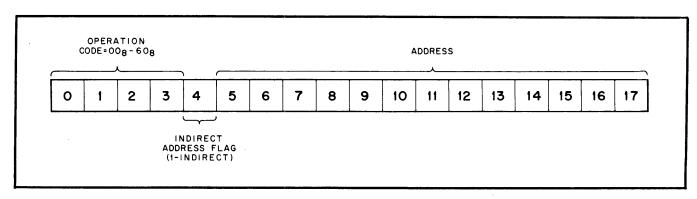

| 7-2         | Augmented Instruction Format                                                 | 7-2          |

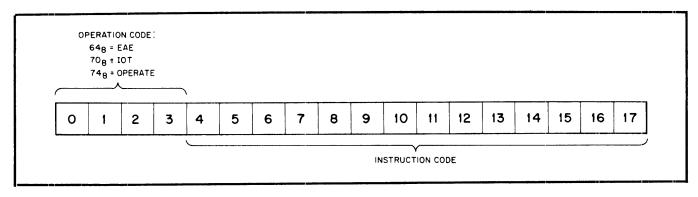

| 7-3         | Operate Instructions                                                         | 7-6          |

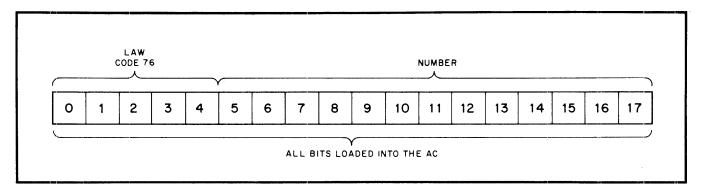

| 7-4         | LAW Instruction_                                                             | 7-8          |

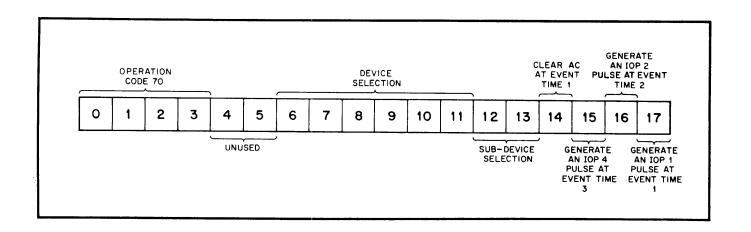

| 7-5         | IOT Instruction Format                                                       | 7-9          |

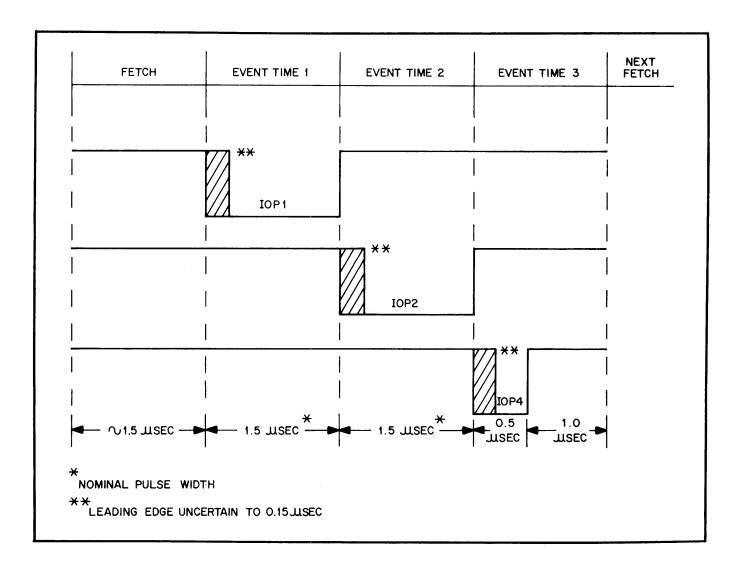

| 7-6         | IOT Instruction Timing                                                       | 7-9          |

| 7-7         | EAE Instruction Formats (Sheet 1)                                            | 7-11         |

|             | EAE Instruction Formats (Sheet 2)                                            | 7-12         |

| <b>7-</b> 8 | EAE Microinstructions                                                        | 7-13         |

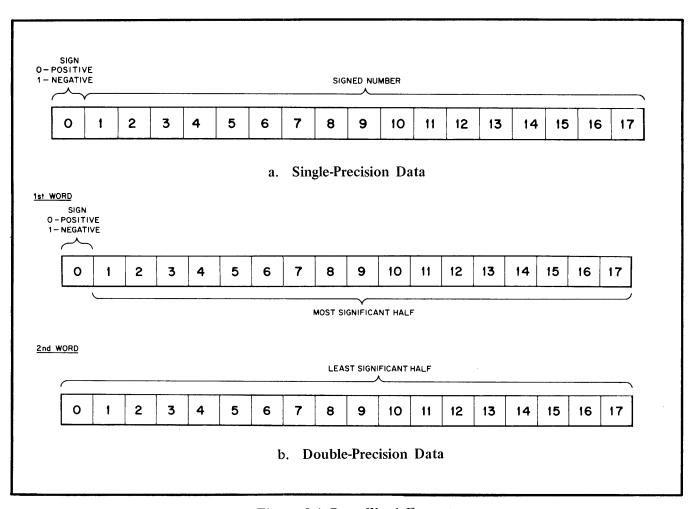

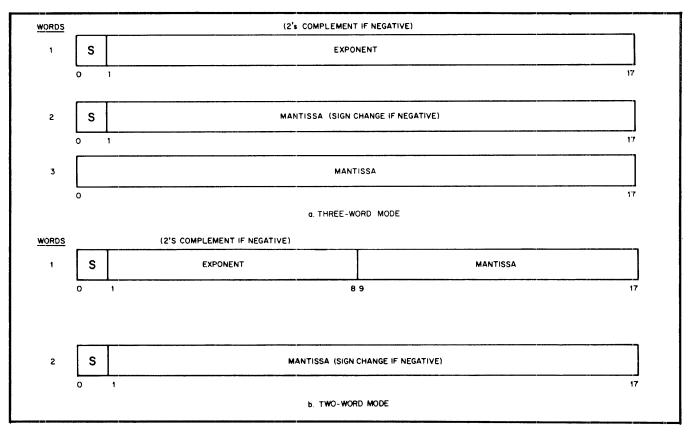

| 8-1         | Data Word Formats                                                            | 8-3          |

| 8-2         | Floating Point Formats                                                       | 8-4          |

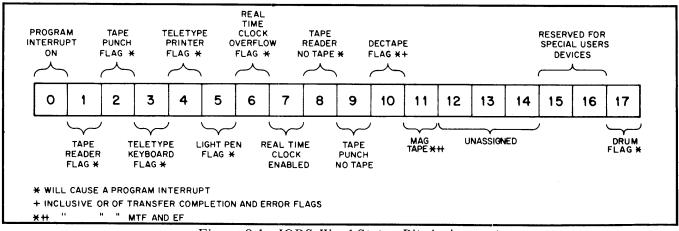

| 9-1         | IORS Word-Status Bit Assignment                                              | 9-3          |

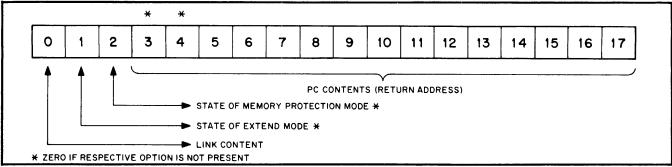

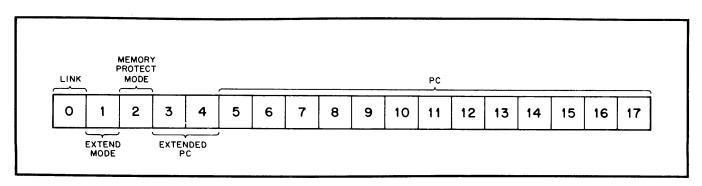

| 9-2         | Program Interrupt, JMS Instruction, or CAL Instruction Storage Word          | 0.5          |

|             | Format                                                                       | 9-5          |

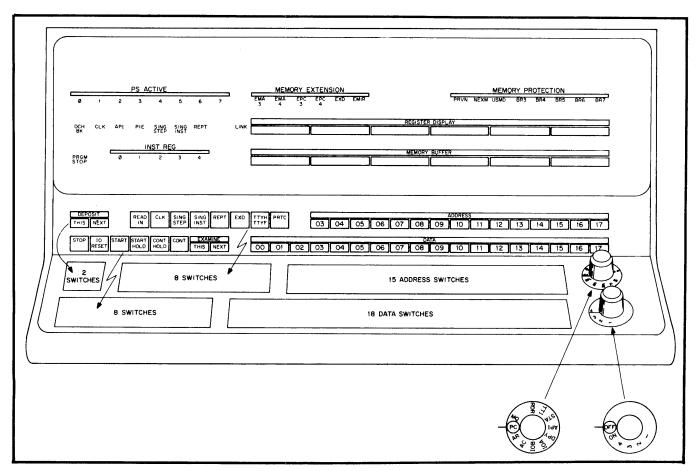

| 10-1        | PDP-9/L Operator Console                                                     | 10-1         |

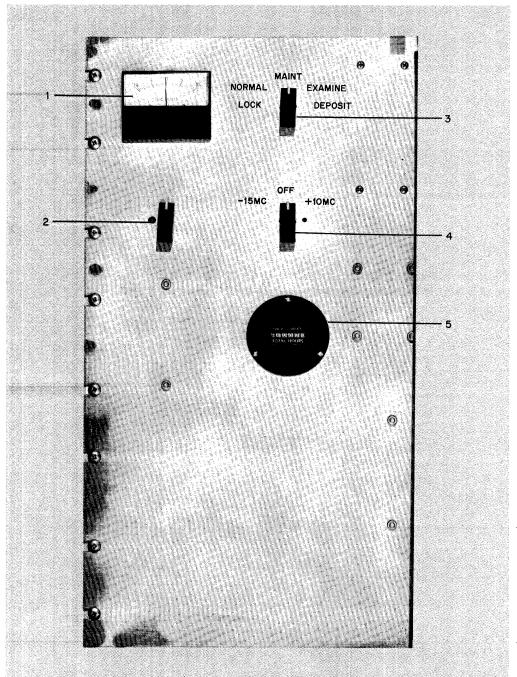

| 10-2        | Marginal-Check Panel                                                         | 10-5         |

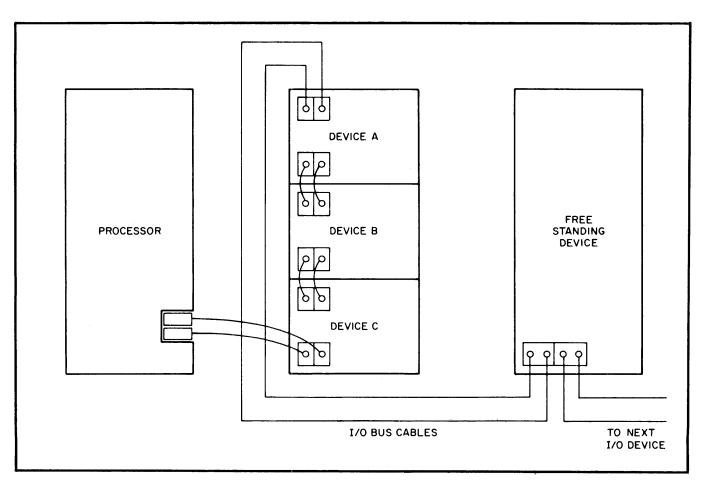

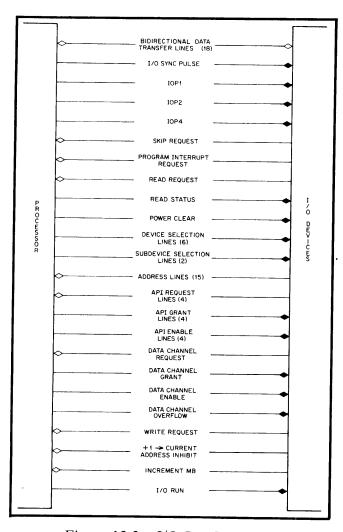

| 12-1        | I/O Bus Connections                                                          | 12-1         |

| 12-2        | I/O Bus Interface                                                            | 12-3         |

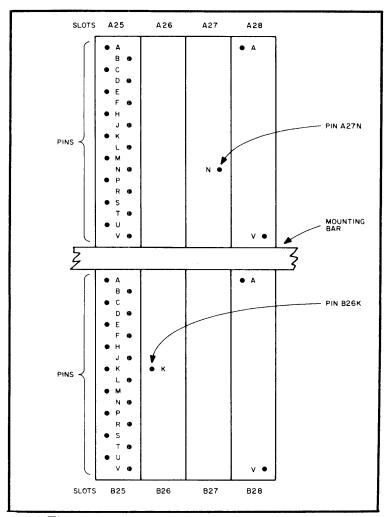

| 12-3        | Interface Connectors and Pins                                                | 12-5<br>13-2 |

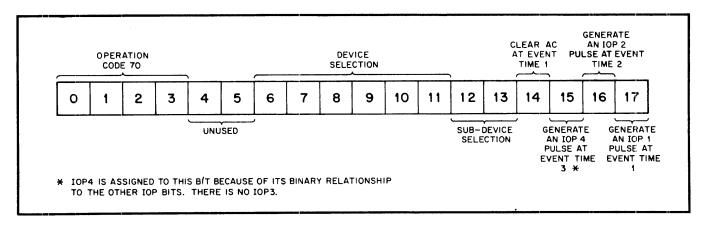

| 13-1        | PDP-9/L IOT Instruction Format                                               | 13-2         |

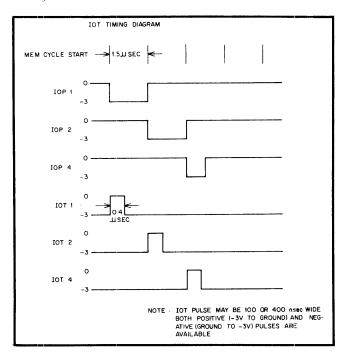

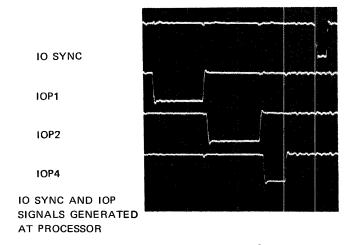

| 13-2        | IOT Timing Diagram                                                           | 13-2         |

| 13-3        | IOT Pulse Waveforms                                                          | 13.4         |

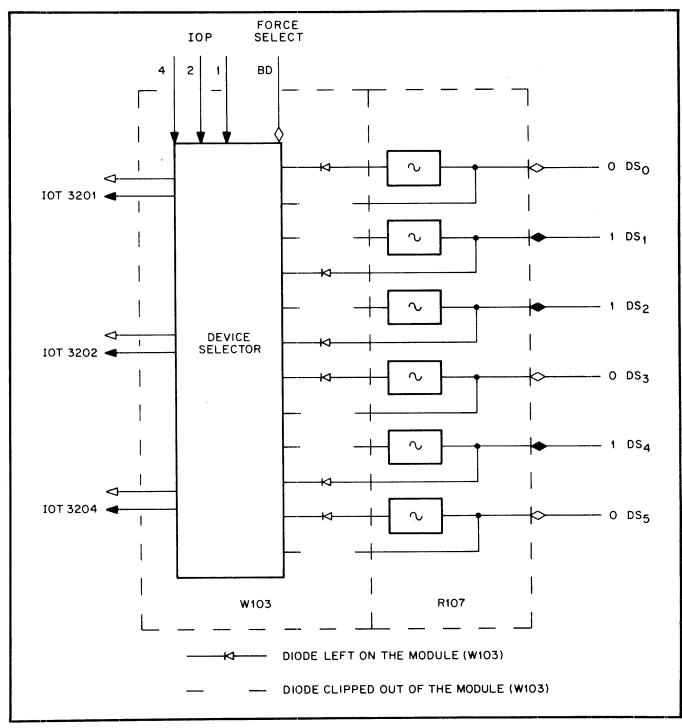

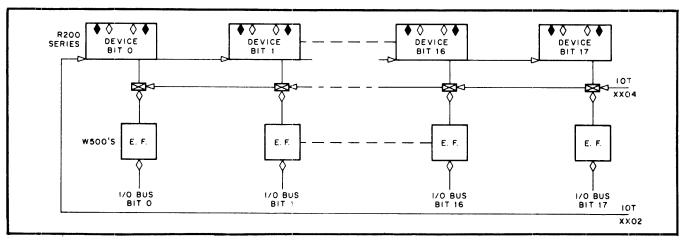

| 13-4        | Device Selector Configurations                                               | 13-5         |

| 13-5        | Loading the AC From a Device Buffer                                          | 13-5         |

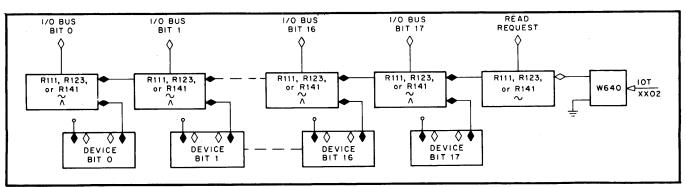

| 13-6        | I/O Signals from Buffer to I/O Bus                                           | 13-5         |

| 13-7        | Loading a Device Buffer from AC                                              | 13-6         |

| 13-8        | I/O Signals from I/O Bus to Buffer                                           | 13-0         |

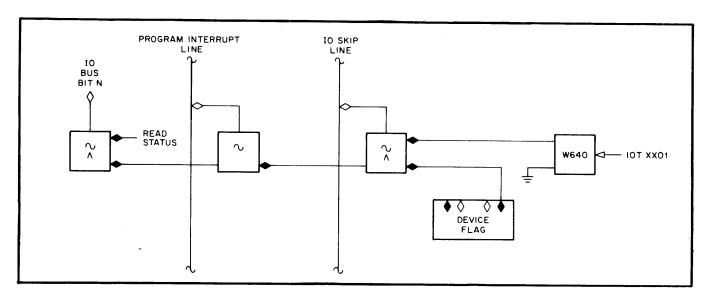

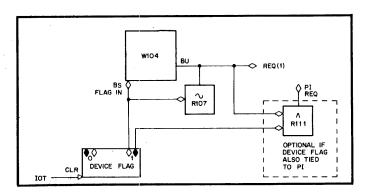

| 13-9        | Device Flag Hardware                                                         | 13-7         |

| 13-10       | Program Interrupt Storage Word                                               | 13-10        |

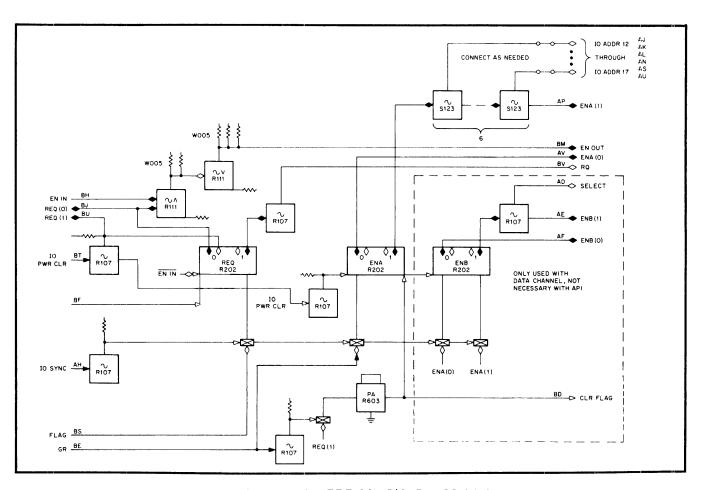

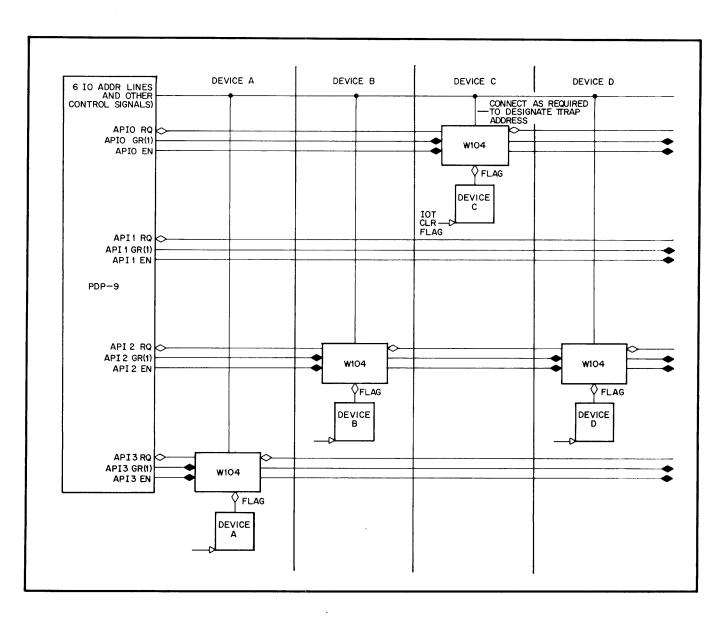

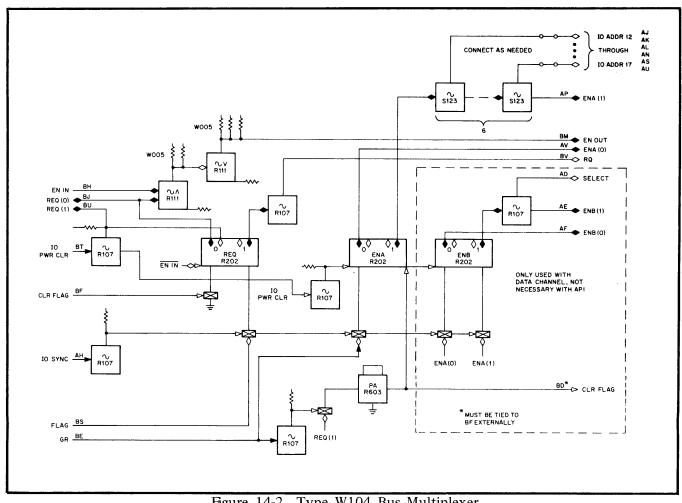

| 13-11       | W104: PDP-9/L I/O Bus Multiplexer                                            | 13-10        |

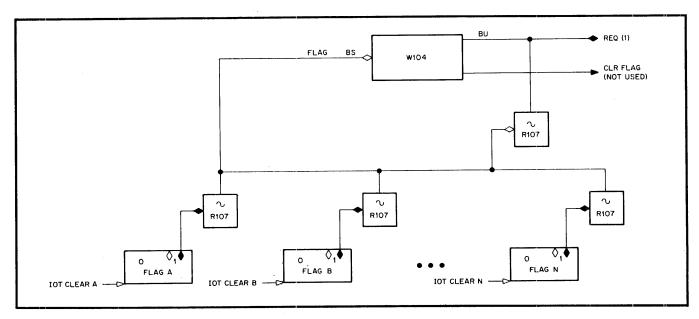

| 13-12       | Devices on the Automatic Priority Interrupt                                  | 13-11        |

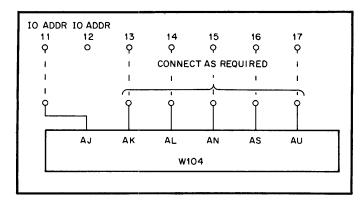

| 13-13       | Connections for Trap Addresses Between 100 <sub>8</sub> and 137 <sub>8</sub> | 13-11        |

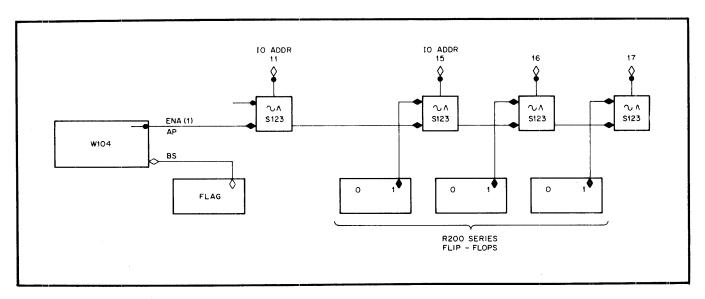

| 13-14       | Gating Flip-Flop Register onto I/O Address Lines                             | 13-12        |

| 13-15       | Interface of a Single Device Flag to both the PI and API                     | 13-12        |

| 13-16       | Single Device with Multiple Flags                                            | 14-3         |

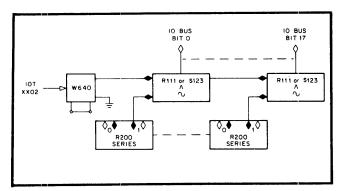

| 14-1        | Data Channel Configuration                                                   | 14-3         |

| 14-2        | Type W104 Bus Multiplexer                                                    | 14-4         |

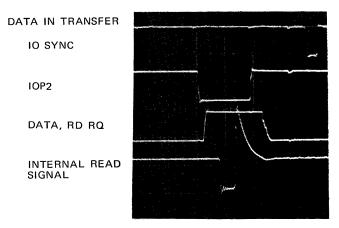

| 14-3        | DCH In Transfer (To Computer)                                                | 14-4         |

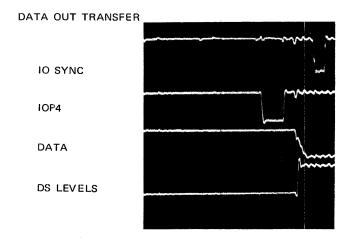

| 14-4        | DCH Out Transfer (From Computer)                                             | 14-6         |

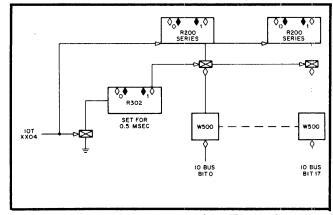

| 14-5        | DCH Timing                                                                   | 15-2         |

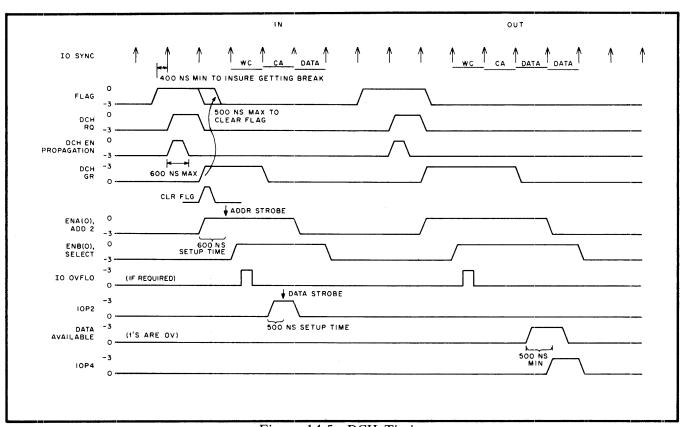

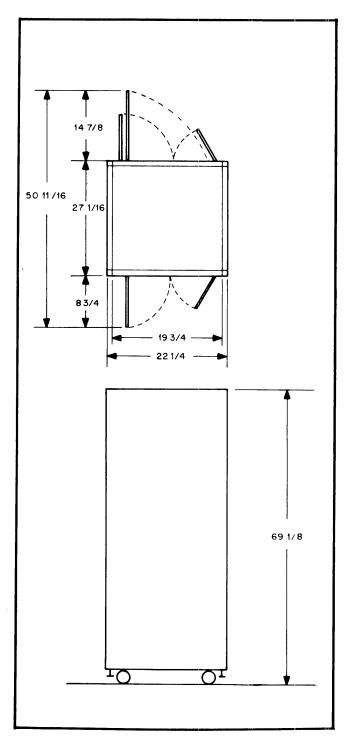

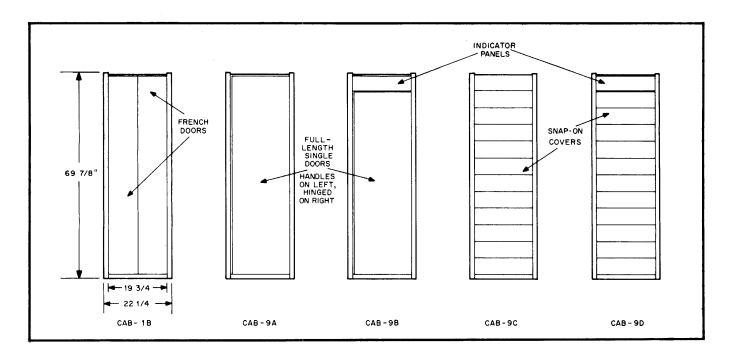

| 15-1        | Basic PDP-9/L Cabinet Specifications                                         | 15-3         |

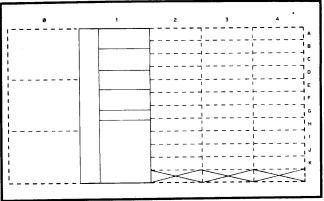

| 15-2(A)     | Basic PDP-9/L (Front)                                                        | 15-4         |

| 15-2(B)     | Basic PDP-9/L (Rear, Back Door Removed)                                      | 15-4         |

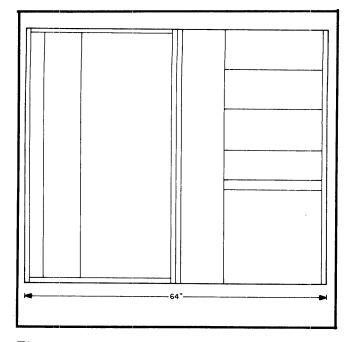

| 15-3        | PDP-9/L With Extra Memories (Front)                                          | 15-4         |

| 15-4        | 19-inch Cabinet Specifications                                               | 15-5         |

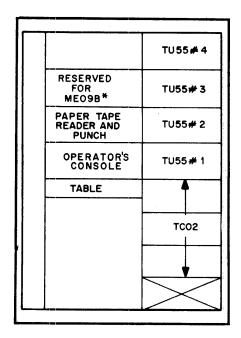

| 15-5        | PDP-9/L With DECtape and PC09A                                               | 15-5         |

| 15-6        | Cabinet Configurations                                                       | 15-6         |

| 15-7        | Basic PDP-9/L with DECtape and PC09A                                         | 15-6         |

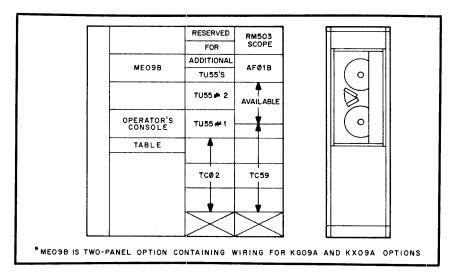

| 15-8        | Memory Expansion and DECtape Expansion                                       | 15-6         |

| 15-9        | Typical PDP-9/L System                                                       | 15-7         |

| 15-10       | Cabinet Configurations                                                       | 10 /         |

# LIST OF TABLES

| Table        | Title                                                                            | Page          |

|--------------|----------------------------------------------------------------------------------|---------------|

| 3-1          | Memory Protection Type KX09A Instructions                                        | 3-7           |

| 4-1          | Keyboard Instructions                                                            | 4-1           |

| 4-2          | Reader Instructions                                                              | 4-2           |

| 4-3          | Teleprinter Instructions                                                         | 4-2           |

| 4-4          | Punch_Instructions                                                               | 4-3           |

| 4-5          | Tape Reader IOT Instructions                                                     | 4-6           |

| 4-6          | Tape Punch IOT Instructions                                                      | 4-7           |

| 4-7          | Card Reader CR02B IOT Instructions                                               | 4-8           |

| 4-8          | Card Reader CR02B, Console Lights, Buttons and Switches                          | 4-9           |

| 4-9          | Line Printer Controls and Indicators                                             | 4-11          |

| 4-10<br>4-11 | Line Printer Type 647E                                                           | 4-12          |

| 4-11<br>4-12 | Digital Incremental Recorder Characteristics                                     | 4-13          |

| 4-12         | Incremental Plotter and Control Instructions                                     | 4-13          |

| 4-13<br>4-14 | Oscilloscope and Precision Display Instructions A/D Converter Characteristics    | 4-15          |

| 4-15         | AF01B A/D Converter and Multiplexer IOT Instructions                             | 4-16          |

| 4-16         | Relay Buffer Commands                                                            | 4-17          |

| 4-17         | Interprocessor Buffers DB99A and DB98A IOT Instructions                          | 4-18<br>4-19  |

| 4-18         | Bit Synchronous Data Communications System Types DP01B and                       | 4-19          |

|              | DP09A IOT Commands                                                               | 4-22          |

| 5-1          | TC02 Control IOT Instructions                                                    | 5-4           |

| 5-2          | DECtape function Summary                                                         | 5-13          |

| 5-3          | DECtape Error Summary                                                            | 5-14          |

| 5-4          | DECtape Timing Data                                                              | 5-14          |

| 5-5          | TC59 Control IOT Instrutcions                                                    | 5-16          |

| 6-1          | Memory Extension Control Instructions                                            | 6-3           |

| 6-2          | Reserved Addresses                                                               | 6-4           |

| 7-1          | EAE Operation Times                                                              | 7-14          |

| 7-2          | EAE Microinstructions                                                            | 7-22          |

| 9-1          | API IOT Instructions                                                             | 9-8           |

| 9-2          | Status Bits Associated With the SPI Instruction                                  | 9-9           |

| 9-3          | Control Bits Associated with ISA Instruction                                     | 9-10          |

| 9-4          | Status Bits Associated With the RPL Instruction                                  | 9-11          |

| 9-5          | Clock IOT Instructions                                                           | 9-13          |

| 10-1         | Operator Console Controls and Indicators                                         | 10-2          |

| 10-2         | Marginal-Check Panel Controls and Indicators                                     | 10-6          |

| 11-1         | Data Transfer Rates                                                              | 11-2          |

| 12-1         | I/O Bus Interface Chart                                                          | 12-5          |

| 13-1         | Assigned PDP-9/L Device Selection Codes                                          | 13-3          |

| 13-2<br>14-1 | Channel and Priority Assignments                                                 | 13-9          |

| 14-1         | Signal Definitions Standard Core Pagister Assignment                             | 14-5          |

| 15-1         | Standard Core Register Assignment                                                | 14-6          |

| 15-2         | PDP-9/L, Extra Memory, Free-Standing Options and Their Controls Wired-In Options | 15-8          |

| 15-3         | Hardware and Logic Options for 19-Inch Cabinets                                  | 15-9<br>15-10 |

|              |                                                                                  |               |

PDP-9/L Programmed Data Processor

# CHAPTER 1 SYSTEM INTRODUCTION

#### **GENERAL**

The PDP-9/L® programmed data processing system is a general purpose computer, incorporating FLIP CHIP hybrid integrated circuits throughout. The PDP-9/L features:

- High performance at low cost

- Demonstrated reliability

- Simple input/output interfacing

- Extensive software

Flexible, high capacity, input/output provisions coupled with a complete line of peripheral equipment allow system planning to satisfy a variety of applications. The PDP-9/L can be easily configured to perform equally well the role of central data processing facility, control element, or satellite processor. The ease with which its modular hardware and software adapt to the requirements of data acquisition, process control, and on-line processing in real-time environments makes it the ideal small scale system for scientific and industrial use.

The PDP-9/L system is a single address, fixed word length (18 bits), parallel binary computer. The minimum system configuration (see frontispiece) has 4096 words of core memory storage, paper tape input and output, console teleprinter keyboard input and printer output at 10-Hz (ASR-33).

The system readily interfaces to optional peripherals such as punched card equipment, line printers, magnetic tape transports, analog-to-digital converters, digital-to-analog converters, CRT displays, data communication equipment, and disk systems. Equipment of special design is easily adapted for interfacing to the PDP-9/L. The FLIP CHIP module line offers proven reliability plus simple, inexpensive fabrication of compatible interface controls for special equipment, or for the special-purpose equipment itself. Peripherals can be interfaced to the system as processing requirements expand, without modification of the central processor.

#### **CHARACTERISTICS**

Complete cycle time of 1.5 microseconds for the random access ferrite core memory.

Real-time clock (option) generates a clock pulse every 16.7 msec (every 20 msec for 50-Hz systems) to increment a time counter stored in system memory. The counter initiates a program interrupt when a programmed preset time interval is completed. The clock can be enabled or disabled under program control.

True direct addressing is provided for 4096 18-bit word locations in the basic core memory module configuration or any memory module containing up to 8129 words appended to the system. The system allows indirect addressing up to the memory expansion limit of 32,768 locations. Core memory is expanded in increments of 4096 words. System software expands to make efficient use of all available core memory storage.

Power failure protection can be optionally implemented to protect against data loss due to internal power interruptions. With this option, the PDP-9/L is unaffected by power interruptions of less than 25 msec duration. In the event of a longer interruption, the option can save the active register contents and automatically restart the interrupted program at a specified address when power is restored. Without the "power failure protection" option, power interruptions of 10 msec duration, or longer, may result in loss of active register contents and memory contents.

Automatic readin is provided of binary-coded programs from paper tape via the ASR-33 paper tape reader when provided. A user-initiated and hardware-implemented control transfers 18-bit words (three tape lines) from tape to a block of sequentially addressed core memory locations and executes the instruction defined by the last word without further user intervention.

<sup>®</sup> PDP is a registered trademark of the Digital Equipment Corporation

A built-in test program, user-initiated and hard-ware-implemented, circulates a self-incrementing count through all central processor registers for the purpose of validating both their operation and the internal transfer paths. The user can monitor and verify register operation by observing the respective register display on the control console.

All input/output transfers are executed in parallel bytes up to 18 bits in length.

Bidirectional input/output bus is provided for program controlled data/command transmissions between the central processor and up to 256 external devices. All program controlled I/O transfers pass through the central processor's accumulator (AC), the 18-bit primary arithmetic register. Memory referencing instructions convey data between the AC and system core memory. IOT (input/output transfer) instructions select appropriate devices and effect the data transfer between the AC and information registers in the devices.

Eight buffered data channels allow fast, nonoverlapping data transmission between system core memory and eight devices interfaced to the I/O bus. Data channel transfers occur via the memory buffer (MB) register in the central processor and do not disturb the contents of other major registers in the processor. Thus, a data channel transfer suspends rather than interrupts execution of the program in progress. The maximum transfer capacity of the data channel facility is between 160,000 and 220,000 words per second, depending on the mix of input and output transfers (each output transfer steals four machine cycles; each input transfer steals three cycles). Provisions are made in system memory for word counter registers and current address registers unique to each data channel.

Program interrupt control frees the program in progress from the necessity of monitoring the status of peripheral devices. The program continues until a device signals a request for service. A subroutine, entered automatically upon the processor's granting of the interrupt request, stores the interrupted program's status, determines the device making the request, and transfers control to the appropriate service subroutine. At completion of the device servicing, the interrupted program is restored to control. The program interrupt control facility is suitable for those peripheral devices having low data rates.

Multilevel automatic priority interrupt option (API) affords immediate access to device handling and data handling subroutines on a ranked priority basis. Of the eight priority levels added by this

option the four higher levels are assigned to device use, and the lower four are assigned to software use. The priority levels are fully nested; i.e., a higher priority request can interrupt inprocess servicing of a lower priority. The restoration of an interrupted service subroutine does not require additional programming considerations. Likewise, the return to an interrupted main program segment is easily implemented.

The granting of priority interrupt requests, at completion of the current instruction, is rated above program and program interrupt activity and below data channel or direct memory access channel activity, or real-time clock counting.

The API system has 32 channels of which 28 are allocated to external device interrupting (hardware priority levels) and 4 are allocated to programmed interrupting (software priority levels). A channel assignment defines the core memory location of the unique entry to an interrupt subroutine. Device channels function independently of priority; up to eight device channels may be assigned to the same priority level. Device channels also may be multiplexed without limit, in which case the channel address defines the entry to a search routine rather than unique entry to one routine.

Additional provisions include dynamic reallocation of device priority level assignments (device control must be designed with logic circuits to accomplish reassignment) and programmed raising of the active interrupt to a priority level higher than the normal assignment, when the situation requires exclusion of interrupt requests at specific priority levels. The API is program enabled or disabled. Specific devices can be inhibited from interrupting by appropriate control inputs to their interfaces.

The basic machine has fixed-point hardware capability and floating-point software capability for performing binary arithmetic in 1s and 2s complement notations. Floating-point software offers choice of 6 or 9 decimal digit precision. The program library supplied includes extensive repertoire of multi- and single-precision subroutines.

Add or subtract (complementary addition) is performed in 3 microseconds with fetch of operand from effectively addressed core memory location. Overflow indication is furnished for 1s complement addition where absolute value of algebraic summed result exceeds capacity of the accumulator (2<sup>17</sup> - 1). Algorithms for 2s complement addition and subtraction treat overflow from accumulator as a carry into a 1-bit register called the link.

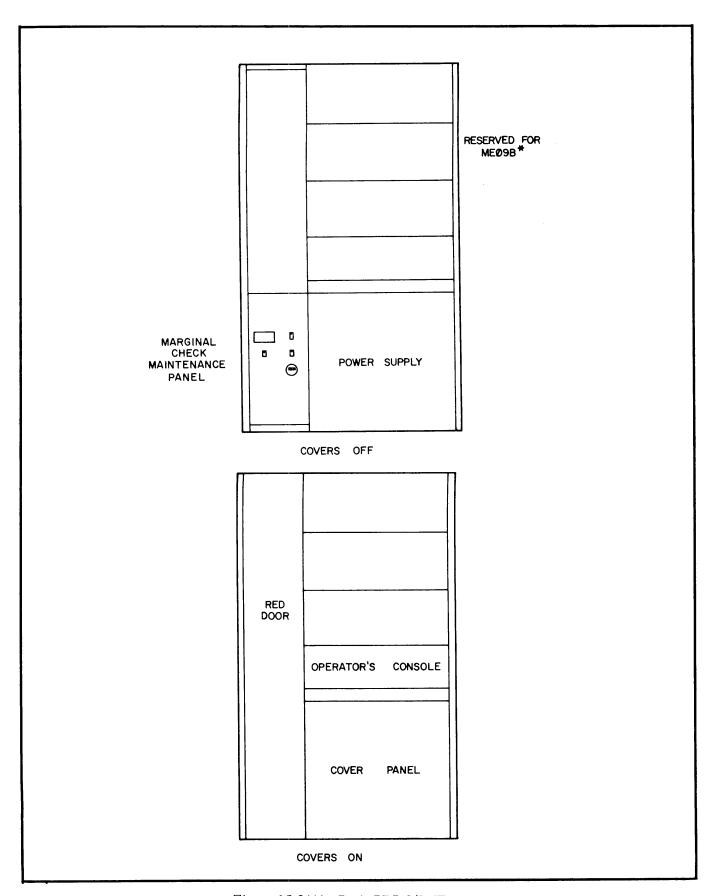

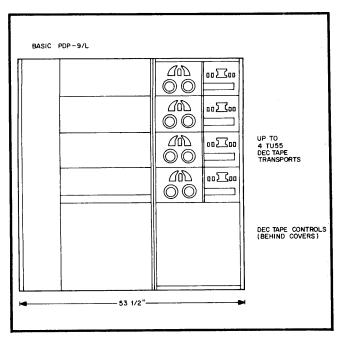

Figure 1-1. Basic PDP-9/L

Extended arithmetic element option offers fast, flexible, hardware execution of the following assigned or unassigned functions:

Shifting the contents of the primary arithmetic registers (AC or MQ), right or left, in 3 to 19 microseconds.

Normalizing the quantity in the primary arithmetic registers; i.e., shifting the contents left to remove leading binary 0s for the purpose of preserving as many significant bits as possible. Time required is 3 to 19 microseconds.

Multiplication in 4.5 to 12.5 microseconds.

*Division*, including integer and fractional, in 4.5 to 13.5 microseconds. Divide overflow indication is furnished when division would produce quotient exceeding 2<sup>17</sup> - 1 magnitude.

#### **DESIGN**

The compactness of the PDP-9/L affords maximum computing facility in a minimum of space; its modular construction provides for ease of system growth to meet future processing requirements—external devices and additional core memory append with minimum effort and no effect on the central processor. (Chapter 4, Peripherals,

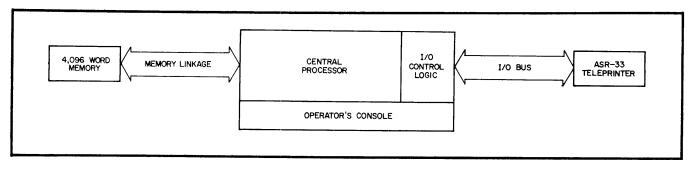

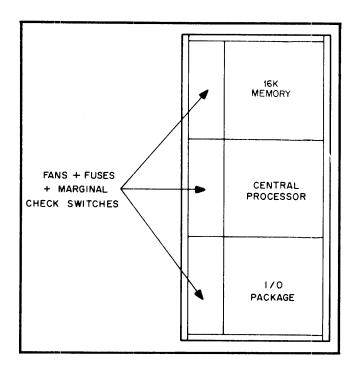

Figure 1-2. Expanded PDP-9/L System Configuration, Block Diagram

presents complete details on interfacing special purpose or user-designed external device to the PDP-9/L input/output facilities.) PDP-9/L is completely self-contained, and does not require special air conditioning or humidity control. Internal power supplies generate all the required power from a 115-volt, 60-Hz, single-phase power source. Systems can be equipped to operate with 50-Hz power at a variety of voltage levels.

#### CONFIGURATIONS

The basic PDP-9/L configuration (figure 1-1) consists of the following.

- 1. Central processor with integrated control console, work shelf and chair.

- 2. Core memory stack of 4096 18-bit words.

- 3. Teletype ASR-33 provides paper tape reader and punch and teleprinter. It operates at 10 character/second. (Teletype Modes ASR-35 can be optionally supplied and is recommended for applications where extreme use is to be made of the teleprinter's output function.)

- 4. Real-time clock (option).

- 5. Input/output facilities: I/O bus, eight data channels, program interrupt control, I/O

status word provision, and conditional skip on external device status.

The PDP-9/L expands into a variety of configurations by:

Adding a 300 character/second paper tape reader and 50 character/second paper tape punch.

Increasing system core memory from the basic-supplied 4096 words up to 32,768 words in increments of 4096 words.

Adding peripheral equipment selected from the PDP-9/L line, or interfacing the system to special purpose or user-designed equipment.

Interfacing a basic expanded PDP-9/L to a data processing complex.

Incorporating central processor options to increase the system's computing and data handling power.

Figure 1-2 illustrates a typical expanded PDP-9/L system.

# CHAPTER 2 SOFTWARE SYSTEMS

#### **GENERAL**

PDP-9/L offers two complete software systems, PDP-9/L COMPACT and PDP-9 ADVANCED, plus an extensive library of arithmetic subroutines, utility programs, and maintenance and diagnostic routines.

The PDP-9/L COMPACT software functions in a paper tape input/output environment (i.e., source and object forms of programs reside on paper tape) with its field-tested components running in standalone fashion to provide the user with powerful single-job capabilities.

The PDP-9 ADVANCED software is an all new package of systems and utility programs, combining the latest concepts in device-independent programming with the power of FORTRAN IV and a macro assembler. PDP-9 ADVANCED software requires 8192 words of memory and is available in the following two compatible versions:

Under control of a simple input/ output monitor for PDP-9/L's with paper tape input/output or card input. This version will greatly expand the single-job capabilities available with PDP-9/L COMPACT software.

In a more sophisticated monitor environment for all PDP-9/L's with some form of auxiliary bulk storage (DECtape, magnetic tape, or disk). This latter version will permit device independent programming under control of a keyboard monitor and a sophisticated input/output programming system.

#### PDP-9/L COMPACT SOFTWARE

#### Assembler

The PDP-9/L Assembler is a two-pass assembly which requires less than 3K of memory. It makes machine language programming on the PDP-9/L much easier, faster and more efficient. It permits the programmer to use mnemonic symbols to represent instruction operation codes, locations, and numeric quantities. By using symbols to identify instructions and data in his pro-

gram, the programmer can easily refer to any point in his program without knowing actual machine locations.

Among the features of the assembler are a powerful set of pseudo operation instructions which are used to:

- 1. Reserve a block of core.

- 2. Set a desired radix.

- 3. Conditionalize sections of coding.

- 4. Output text strings.

- 5. Control the listing produced by the assembler.

The assembler also allows the user to replace symbolic data references by representing them as literals. The PDP-9/L assembler is upward compatible with MACRO-9 at the source language level. Input and output devices may be assigned by communicating with the assembler.

#### Symbolic Editor

The symbolic editor of the PDP-9/L software system provides the user with the ability to conveniently create, examine and modify symbolic ASCII text material. The editor operates on lines of symbolic text, delimited by carriage return characters and organized into pages or blocks. These lines can be read into a buffer, selectively examined, deleted, or modified, and written out. New text may be substituted, inserted or appended.

Editor operation codes are divided into two basic categories: control instructions and editor commands. Control instructions determine the editor's operation level: input text or edit text. The input text level is used to create new symbolic material. The edit text level uses the editor commands which fall into four classes: I/O requests, pointer manipulation, editing requests, and examination requests. The pointer is a software device which places the current line in a special work area of core to facilitate edit request processing.

The editor is most frequently used to modify PDP-9/L source programs, but may be used to edit any symbolic ASCII text. It operates with all standard PDP-9/L peripheral devices.

#### ODT-9

ODT-9 (Octal Debugging Technique) is a powerful program checkout aid which allows the user to carry on an interactive on-line debugging process with teletype commands and octal numbers. As errors are found, they may be corrected on-line and then the program can be executed immediately to test the correction. In general, the user types commands to ODT-9 which control the following functions:

- 1. Initiating the user's program.

- 2. Stopping and subsequently continuing the user's program at selected points called *breakpoints*.

- 3. Examining and/or modifying the accumulator and link at breakpoints.

- 4. Examining and/or modifying the contents of any memory location.

- 5. Searching user defined areas for memory locations containing specific bit configurations.

- 6. Dumping areas of memory for later loading, debugging and execution.

#### **TRACE-9**

TRACE-9 is an on-line debugging tool which allows the user to trace the execution of specified portions of his program. In general, TRACE-9 generates a listing on the teleprinter which details the flow of control as the program executes. The information printed includes, for each traced instruction, the location of the instruction, the instruction itself, the location of the next instruction to be executed, and the values in the accumulator and link after execution of the instruction. TRACE-9 is controlled through teletype commands which specify tracing parameters such as:

- 1. Start address for tracing.

- 2. Stop address for tracing.

- 3. Various counts to specify when to start and stop.

Teletype commands may also be used to specify functions such as:

- 1. Suppressing the accumulator printout.

- 2. Printing only on CAL, JMS, JMP and SKIP instructions.

- 3. Tracing the program interrupts.

- 4. Halting or continuing the user's program upon completion of the trace.

#### **SCAN**

SCAN is a small program used to scan areas of memory for particular bit configurations. The user specifies the start and stop address for the area to be scanned, the bit configuration to look for, and the bit positions to be tested (i.e., a mask). SCAN then scans the area. When a match is found, the address of the match is printed along with the unmasked matching word. Proper selection of the operating parameters allows SCAN to be used as a dump.

#### **FAST-9**

FAST-9 (Fast Acquisition of System Tape) is a loading system for use in the PDP-9/L Software System to retrieve frequently used programs from DECtape and to create system tapes. The main advantages of the system are speed and ease of access.

The FAST-9 system tape, as distributed by DEC, contains commonly used Software System programs such as the Symbolic Editor, the PDP-9/L Assembler and ODT. Since these can be called from DECtape with only a small bootstrap, papertape handling is eliminated for systems programs. This results not only in a significant time savings, but also in increased reliability. FAST-9 is by no means restricted to Digital systems programs; it can very conveniently by employed for frequently accessed user created programs. This manual contains complete directions for use of the FAST-9 system tape as well as directions for adding user programs to the system.

#### **HRM-Puncher**

The HRM Puncher is a self-relocating paper tape dump program. It may be loaded, by the Hardware Read-in (HRI), into any block of memory. It relocates itself and then punches out a user specified area of memory in the HRI format.

#### Floating Point Package

These routines perform all arithmetic operations on normalized floating point data. The routines must be assembled with the user's program. He can use either single (20-bit accuracy) or double (35-bit accuracy) precision data. The actual arithmetic is performed using software accumulators by program FPOINT. Programs SINGLE and DOUBLE are required to perform the setup for FPOINT.

#### Integer Arithmetic

These routines provide PDP-9/L users, without the EAE option, with simulated logical and signed multiply and divide routines.

#### FLIO (Floating Input/Output)

These routines allow the user to input and output signed decimal data in floating point format, from either the teletype or paper tape reader.

#### TOD (Teletype Octal Dump)

The TOD allows the user to obtain a typed output of the contents of any register or set of registers he specifies. This program is provided in two versions one for loading into high core (start at 7602) and one for low core (start at 22).

#### TTYIO (Teletype Input/Output Conversion)

This package consists of routines which allow text to be input and output through the teleprinter. Formatting routines are also available in this package.

# DIP-OPS (Decimal Integer Print/and Octal Print Subroutines)

Allows the user to output his data to the teleprinter in any of four modes: 1) signed decimal, 2) right justified octal, 3) left justified octal, and 4) octal with no zero suppression.

#### **PTLIST**

This routine lists a paper tape from either the paper tape reader or the keyboard, and prints it on the teletype.

#### MTDUPE (Master Tape Duplicator)

The MTDUPE duplicates and verifies tapes. The MTDUPE duplicates any tape. By using switches the user is allowed to have a title punched in a readable format. The verifying routine checks the parity and will stop at every frame where the parity is off.

#### **Trig Functions**

These routines allow the PDP-9/L user to perform trigonometric calculations on his floating point data in either single or double precision mode.

#### PDP-9 ADVANCED SOFTWARE

PDP-9 ADVANCED software is an all-new completely relocatable software package combining sophisticated programming features with flexibility and ease of use. This new package includes a FORTRAN IV compiler, a macro assembler, an on-line debugging system, a symbolic editor, a peripheral interchange program, a linking loader, an input/output programming system, and a monitor.

Two versions of the PDP-9 ADVANCED software system are available: a simple input/output monitor system with 8K and paper tape input/output (using optional PC09A) and the option of punched card input facilities for basic PDP-9 users. The system will also include a more sophisticated monitor-based, device-independent system for PDP-9s with one or more forms of auxiliary bulk storage (magnetic tape, DECtape, or disk). Both systems are compatible.

#### Paper Tape (or Card) System

Basic or extended-memory PDP-9/L systems without auxiliary bulk storage use the FORTRAN IV compiler, macro assembler (MACRO-9), debugging system (DDT-9), Symbolic Editor, peripheral Interchange Program (PIP-9), and Linking Loader under the control of the Input/Output Monitor. Only paper tape input/output or card input is provided. All systems programs have full features, are completely relocatable, and handle or produce relocatable code. Maximum utilization will be made of optional central processor features, such as the Extended Arithmetic Element and Automatic Priority Interrupt, when they are available.

#### **Device-Independent System**

The inclusion of bulk storage in a PDP-9/L will allow the use of the keyboard monitor-based, device-independent version of PDP-9 ADVANCED software. The minimum bulk storage requirements are:

- DECtape transports (TU55) and control (TC02), or

- 2 IBM-compatible transports (TU20 or equivalent) and control (TC59), or

- 1 disk system and control

With the addition of one of these forms of bulk storage to a PDP-9/L system, the Keyboard Monitor (KM-9), and the Input/Output Programming System (IOPS) can be used to automatically store, retrieve, load and execute PDP-9 programs. With this device-independent version of PDP-9 ADVANCED software, the user can call his system programs from any bulk storage device (designated the system device), compile or assemble from any input device to any proper output device, and (optionally) obtain listings on any printing device or magnetic tape. By using the keyboard monitor to change the system and object program device assignment tables, the operator may designate at load time which devices shall serve as system device, object program storage, and data input and output devices. The linking loader, with access to the input/output programming system, automatically loads the input/output programs required by the device assignment tables.

#### **System Components**

The component packages of the new PDP-9 ADVANCED software system are described briefly below. More complete descriptions will be found in the individual language specification or operator's manual for each program.

#### FORTRAN IV

The PDP-9 FORTRAN IV compiler is a two-pass system which accepts statements written in the FORTRAN language and produces relocatable object code capable of being loaded by the linking loader program. It is fully compatible with USA FORTRAN IV, as defined in the USA Standard X3.9-1966, with the exception of the following few features which were modified to allow the compiler to operate in 8,192 words of core storage:

1. Complex arithmetic will not be available.

- 2. Adjustable array dimensions will not be allowed.

- Blank COMMON will be treated as named COMMON.

- 4. The implied DO feature will be deleted from the DATA statement.

This FORTRAN IV compiler operates with the PDP-9 program interrupt facility enabled and generates real-time programs that both operate with the program interrupt enabled and can work in conjunction with assembly language programs that recognize and service real-time devices. Subroutines written in either FORTRAN IV or the Macro Assembler language can be loaded with and called by FORTRAN IV main programs. Comprehensive source language diagnostics are produced during compilation; a symbol table is generated for use in on-line debugging.

#### Macro Assembler (MACRO-9)

With the Macro Assembler, PDP-9/L users are able to utilize highly sophisticated macro generating and calling facilities within the context of a symbolic assembler. Among the more prominent features of MACRO-9 are:

- 1. The ability to define and call nested and recursive macros.

- Conditional assembly based on the computational results of symbols or expressions.

- 3. Repeat functions.

- 4. A variety of fixed- and floating-point symbolic formats for constants.

- 5. Boolean manipulation.

- 6. Optional octal and symbolic listings.

- 7. Three forms of radix control (binary, octal, decimal) and two text modes (ASCII and 6-bit trimmed ASCII).

- 8. Global symbols for easy linking of separately assembled programs.

- 9. Choice of output format: relocatable, absolute binary (checksummed); full binary (unchecksummed), capable of being loaded via the READ IN key (console).

- 10. Ability to call input/output system macros which expand into IOPS calling sequences.

#### Debugging System (DDT-9)

DDT-9 adds the flexibility of relocatability and real-time operation to the capabilities of PDP-9 BASIC DDT. With it, the user may load and operate his program in a real-time environment while maintaining strict control over running of each section. DDT-9 allows the operator to insert and delete break-points, examine and change registers, patch programs, and search for specific constants or word formats.

The DDT breakpoints features allow for the insertion and simultaneous use of up to four breakpoints and any one or all of these breakpoints may be removed with a single keyboard command. The search facility allows the operator to specify a search through any part, or all of an object program with printout of the locations of all registers that are equal (or unequal) to specified constant. This search feature also works for portions of words as modified by a mask.

With DDT-9, registers may be examined and modified in either instruction format or octal code, and addresses may be specified in symbolic relative, octal relative, or octal absolute. Patches may be inserted in either source language or octal.

#### **Symbolic Editor**

The Symbolic Editor of the PDP-9 ADVANCED software system provides the ability to read symbolic text from any input device (paper tape reader, card reader, disk, drum, DECtape, magnetic tape, etc.), to examine and correct it, and to write it on any output device. It can also be used to create new symbolic programs.

The Editor operates on lines of symbolic text, delimited by carriage return (C/R) characters and organized into blocks or pages. These lines can be read into a buffer, selectively examined, deleted, or modified, and written out. New text may be substituted, inserted, or appended. Among the types of caommands available to the operator through the Symbolic Editor are:

#### 1. Input Operations

- a. Read a page of text.

- b. Read n lines of text.

- c. Skip a page of text.

- d. Skip n lines of text.

#### 2. Examination Operations

- a. Print the entire buffer.

- b. Print n pages

- c. Print lines n through m.

- d. Print line n.

- e. Print the entire buffer without comments.

- f. Print lines n through m without comments.

- g. Print line n without comments.

- h. Search for and print the next location symbol.

- i. Back up and print the previous line.

### 3. Editing Operations

- a. Delete line n.

- b. Delete lines n through m.

- c. Append text.

- d. Insert text before line n.

- e. Change line n.

- f. Change lines n through m.

- g. Read the next n lines and insert them after line m in the buffer.

- h. Erase the buffer.

- i. Move a line.

# 4. Output Operations

- a. Output the entire buffer.

- b. Output line n.

- c. Output lines n through m.

- d. Punch a form feed.

Several commands which combine input and output commands are also available to the user. With these, the buffer may be cleared and a new page automatically read in after the output of an edited page, or one or more pages may be read and punched in one operation (for duplication of sections of a symbolic tape).

#### Peripheral Interchange Program (PIP-9)

The primary function of PIP-9 is to facilitate the manipulation and transfer of data files from any

input device to any output device. It can be used to update file descriptions, delete, insert, or combine files, perform code conversions, rewind tapes, and retrieve storage space that is no longer required by a file device.

#### **Linking Loader**

The Linking Loader has the task of loading any PDP-9 FORTRAN IV or MACRO-9 object program which exists in relocatable or absolute format. Among its tasks are loading and relocation of programs, loading of called subroutines, retrieval and loading of implied subroutines and IOPS routines, and loading and relocation of the necessary symbol tables.

#### Input/Output Programming System (IOPS)

IOPS provides a standardized programming interface to all input/output devices in a PDP-9/L system. Symbolic input/output unit assignments allow users' programs to select I/O devices specified symbolically to the macro assembler or the FORTRAN IV compiler. IOPS consists of a modular collection of relocatable input/output and utility subroutines which transmit data to and from peripheral devices and make data readily available for processing. IOPS data and file handling routines include device independence for all systems programs.

Specifically, IOPS provides the user with three levels of I/O programs.

- 1. Device handling providing the basic subroutines to allow the user to operate a device, doing code conversion where required.

- 2. Data handling providing the data buffering and internal line and character transmission facilities.

- 3. File handling providing for the manipulation of named files on the system level.

IOPS completely eliminates the need for the programmer to program the standard peripheral devices. The programmer is no longer concerned with input/output problems such as timing, overlap, and the differences in the characteristics of peripheral devices. This permits him to concentrate on his primary task, the processing of data inside the computer.

IOPS is coded on a modular basis to allow addition of new devices and modifications to the handling of current devices. It requires considerably less effort to modify an IOPS subpro-

gram than to revise individual input/output sections to fit a new configuration. By the use of IOPS, programs can be changed more rapidly to fit the expanding configurations.

#### Input/Output Monitor

The simple input/output monitor includes the device assignment tables and input/output routines necessary for programs being run on PDP-9/L's without bulk storage. The function of the monitor is to handle all input and output for system programs or users' programs so that the programmer need not be concerned with device or data manipulation routines. Normally only paper tape input/output or card input is allowed by the input/output monitor.

#### **Keyboard Monitor (KM-9)**

The Keyboard Monitor allows convenient single job processing through commands to the console teleprinter. Its primary functions are: to allow the user direct and immediate access to system user programs stored on bulk storage devices; to facilitate the creation and storage of new programs by the user; and to allow input/output device-independent programming with "load-time" specification of peripherals.

KM-9 consists of bootstrap loader, a keyboard listener program, a monitor command decoder, IOPS routines, an error diagnostic program, and device assignment tables (DATs).

The bootstrap loader always resides in upper memory and is responsible for loading the monitor into lower memory. Return calls from system or user programs cause restoration of control to the Monitor. The keyboard listener (KLIST) accepts input commands from the teletype and handles Monitor initialization and bookkeeping.

The Monitor command decoder (MCD) recognizes requests for system programs and loads the system loader to bring in the requested program. In response to keyboard commands, it also manipulates the device assignment tables to provide the device-independent programming features. The Monitor IOPS include data handling subroutines, and device handlers and interrupt service routines for the Teletype keyboard and printer. The routines for the system device will also be present with the Keyboard Monitor, but all other IOPS routines will be stored on the system device until required by object programs.

The monitor also contains device assignment tables. The purpose of the DATs is to relate

logical I/O units to the actual hardware devices. Each input or output reference within a system or user program refers to a position in a device assignment table. This table, in turn, contains a device assignment for each table entry that may be used. Since the contents of the tables can be altered by commands to the Keyboard Monitor, actual I/O devices may be changed without altering the program references to these devices.

# Expansion of PDP-9 ADVANCED Software System

The above-mentioned features of the PDP-9 AD-VANCED software system are available at this time. Included in the initial system design, but not scheduled for completion until November 1968 are:

Time-shared use of the PDP-9/L by a protected priority foreground program and unprotected system or user background program. This feature will utilize a background/foreground monitor and will require 16,384 words of core, bulk storage, and the memory protection option.

Batch processing from any peripheral device, including the ability to accept monitor commands from any system input device.

Although these features will not be available with the initial versions of PDP-9 ADVANCED software, all necessary provisions have been made for them in the system programs.

#### MAINDEC DIAGNOSTIC PROGRAMS

MAINDEC diagnostic programs are provided for locating hardware malfunctions within the processor, memory, and I/O equipment.

These programs are designed to make troubleshooting fast and straightforward by selectively exercising every circuit in the machine. Instructions and procedures for loading, operating, and interpreting the results of diagnostic tests are written in clear, simple language, so that beginning maintenance technicians can use them easily.

Detailed error messages are printed out to tell the technician exactly which instruction, or bit configuration, has failed. Error codes direct the troubleshooter to specific modules when a fault condition is detected.

The program consists of two parts: the Basic Processor Test and the Extended Processor Test. The Basic Test incrementally checks the entire instruction repertoire, performing 1500 unique tests, and in each case, halts with specific instructions for the troubleshooter. If the Basic Test fails to detect the trouble, the Extended Test uses random number techniques to test the logic for many combinations of data manipulation and addressing problems, runs memory test patterns, performs system tests on I/O devices and controls, and many other tests.

A valuable tool for check-out and troubleshooting, MAINDEC diagnostics contribute to the high productivity of the PDP-9/L by minimizing downtime.

# CHAPTER 3 SYSTEM ORGANIZATION

#### **GENERAL**

The major functional components of the PDP-9/L system are the central processor, core memory, and input/output facilities. This chapter discusses these components and the options offered for each.

#### CENTRAL PROCESSOR UNIT

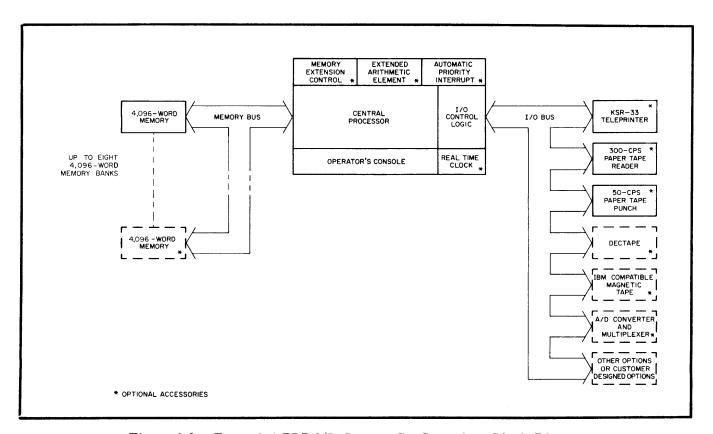

Figure 3-1 illustrates the internal organization of the PDP-9/L central processor. Employing a transfer bus system, data is jam-transferred between registers at DC levels to minimize timing problems (level logic is used instead of pulse logic in the central processor). All active registers use simple circuit designs (no logic delays).

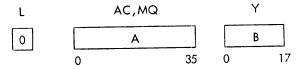

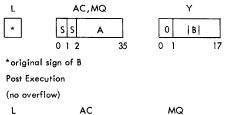

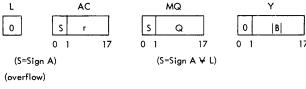

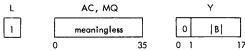

Figure 3-1. Central Processor-Major Register Organization

Control Elements (not illustrated) that govern the gating of information transfers include:

Instruction Register (IR) - The IR accepts the five most significant bits of each instruction word fetched from memory. The four most significant bits constitute the operation code and, when decoded, indicate the entry point to the control memory microinstruction sequence necessary to effect system response. The fifth bit signals

when the fetched instruction indicates indirect addressing.

Control Memory (CM) - The CM stores all sequences of internal microinstructions required to fetch and execute a program's instructions, to effect operation of the data channels, and to respond to operator commands initiated at the control console. It is a very fast, read only, magnetic-core storage unit, prewired with the sequences.

Control Register (CR) - The CR delivers gate control signals to the transfer busses and to the active registers. The register supplies new address information to the CM based on conditions sensed.

Major registers in the processor are:

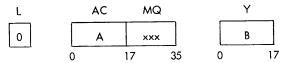

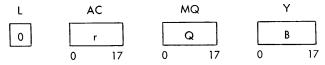

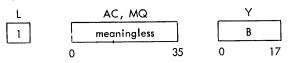

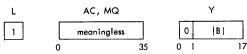

Adder (ADR) - The 19-bit ADR functions as a fast adder for arithmetic operations, and as the transfer path for all inter-register transfers and shift operations. It also increments the PC and MB registers, as required. Entry to the ADR is via the A bus and/or the B bus, under control of CR-developed gating control levels. The ADR operates at a 5 mc rate to provide an inter-register transfer time of 200 nsec.

Accumulator (AC) - The AC, an 18-bit register, retains the result of arithmetic/logical operations for the interim between instructions. The AC can be cleared and complemented. Its contents can be rotated right or left with the link. The contents of the memory buffer register can be added to the contents of the AC with the result left in the AC. The contents of both registers can be combined by the logical operations AND and exclusive OR, the result remaining in the AC. The inclusive OR can be formed between the AC and the Data switches on the operator console and the result left in the AC. For all program controlled transfers, information is transferred between core memory and an external device through the accumulator.

Link (L) - This 1-bit register is used to extend the arithmetic capability of the accumulator. In 1s complement arithmetic, the link is an overflow indicator; in 2s complement arithmetic, it logically

extends the AC to 19 bits and functions as a carry register. The program can check overflow into the link from the accumulator to greatly simplify and speed up single and multiple precision arithmetic routines. The link can be cleared and complemented and its state sensed independent of the AC. It is included with the AC in rotate operations and in logical shifts.

Arithmetic Register (AR) - The AR functions with the AC to perform arithmetic and logical operations. It is not accessible to the programmer. Its operation is a function of the micro-instruction sequences in the CM.

Multiplier-Quotient Register (MQ) - The optionally implemented extended arithmetic element (EAE) adds the logic of the MQ to the basic PDP-9/L. The MQ is 18 bits long and holds the multiplier during multiplying instructions and receives the low-order 18 bits of the resulting product. During division operations it holds the low-order 18 bits of the dividend and, at the completion of the divide instruction, it contains the quotient. It can also be used an an extension of the AC for 36-bit shift operations and for data normalizing operations.

Program Counter (PC) - The PC determines the program sequence; that is, the order in which instructions are performed. This 13-bit register contains the address of the memory cell from which the next instruction is to be taken. Addition of the memory extension control option expands the PC to 15 bits for the addressing of up to 32,768 locations.

Memory Buffer Register (MB) - All information transferred into or out of core memory passes through the 18-bit MB. Information is read from a memory cell into the MB and rewritten into the cell in one cycle time. Instructions and data are brought from core memory into the MB for processing. The MB serves also as a buffer for information transferred between core memory and an external device in data channel transfers.

#### **CORE MEMORY**

The PDP-9/L utilizes a 4-wire 30-stack core memory with a complete cycle time of 1.5 microseconds. Each 4,096 word core memory module contains a core stack, sense amplifiers, drivers, and a memory address (MA) register. The MA sets up the memory location (address) to be used for data retrieval or storage.

System core memory can be expanded from the basic 4,096 words up to 32,768 words in 4,096 word increments. Expansion beyond 8,192 words requires implementation of the optional Memory Extension Control, Type KG09A to extend the PDP-9/L addressing capability.

#### INPUT/OUTPUT FACILITIES

The following text briefly describes the input/output facilities provided with the PDP-9/L in its minimum (basic) configuration. Detailed descriptions concerning the operation and use of these facilities are presented in chapter 9, Input/Output Operations.

Basic PDP-9 I/O facilities include:

- 1. A I/O bus system which chain links all the device controls for all peripheral devices to the central processor unit (CPU).